Short abstract:

Building also upon charge collection mechanisms studied by ESR4 the focus is to develop a so far not existing complete numerical simulation chain in order to predict the reliability of a given CMOS digital circuit in a particular radiation environment representative of a specific application (ground level, space, high energy physics, etc.). Furthermore, a general methodology based on such a numerical simulation chain to harden a device by adjusting, for instance, its layout. The main investigated effects will be Single Event Upset (SEU) in SRAM and Single Event Transient (SET) in typical CMOS circuits such as an inverter chain, adders, multipliers, data-path operators, etc. The study will also provide useful insight for ESR6 and ESR11, as well as a tool to be used by ESR5. More generally, it will improve design capabilities of rad-hard components at an industrial level, significantly reducing the development time and cost.

Long abstract:

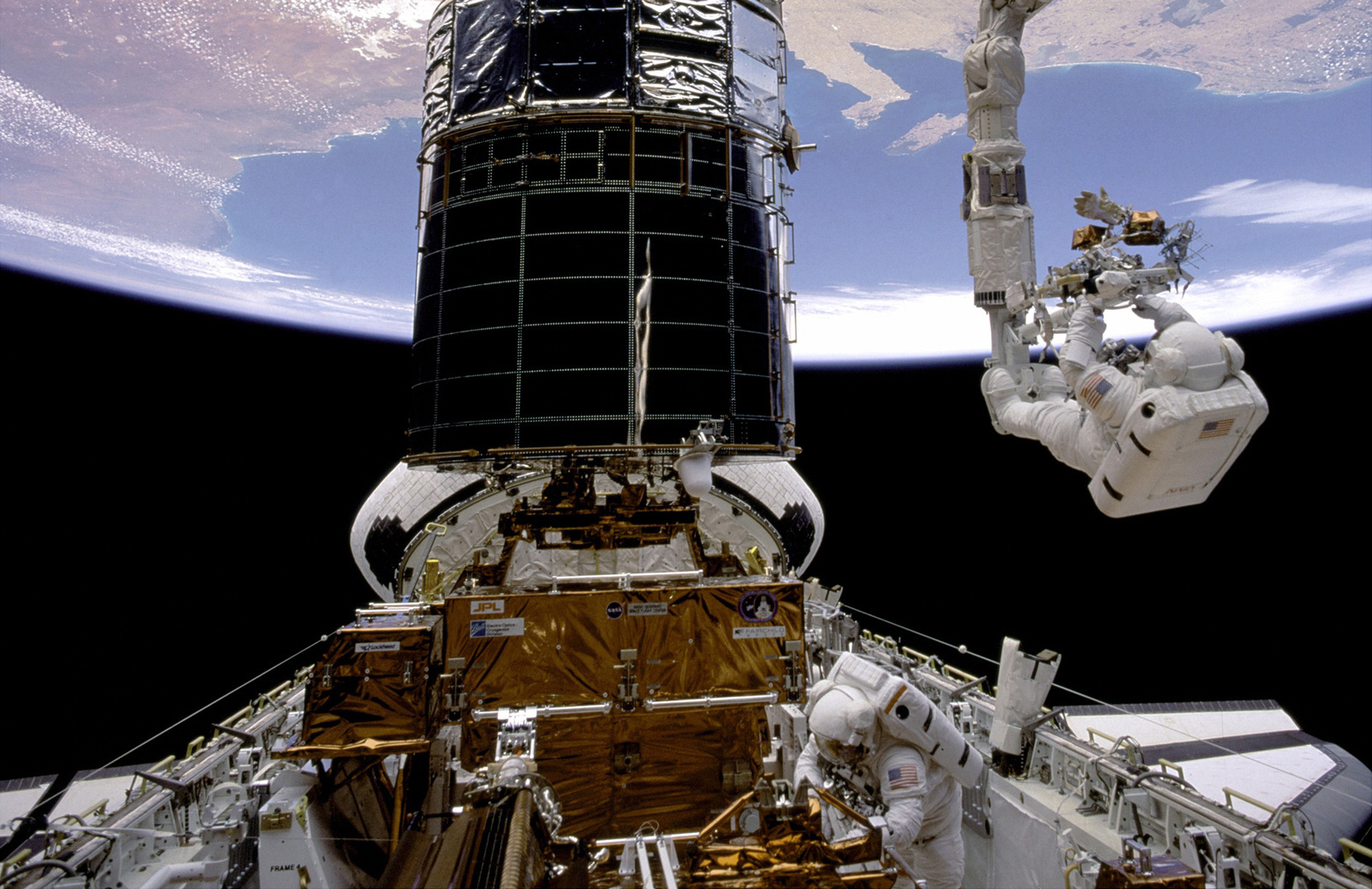

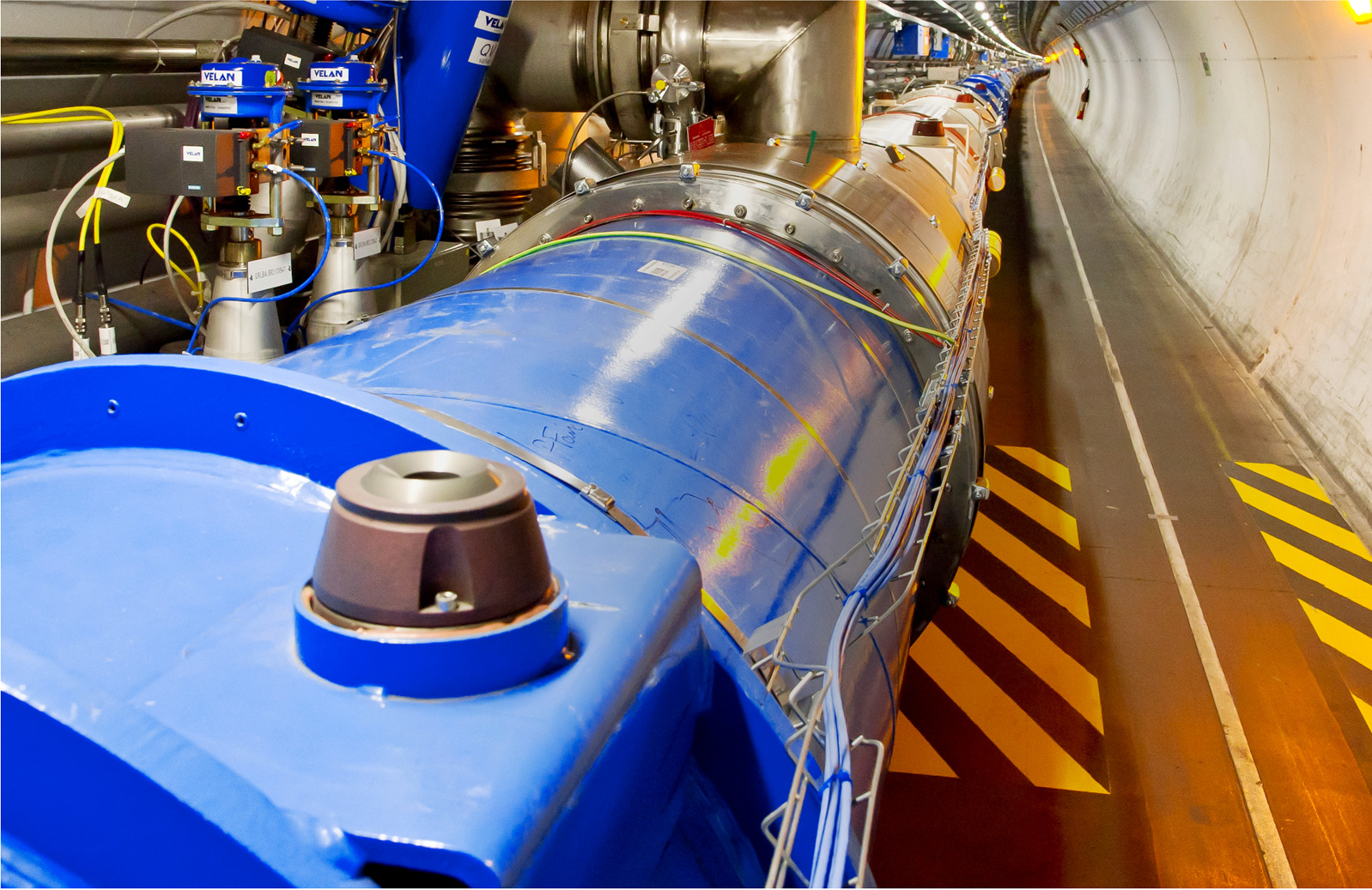

This PhD will first focus on the complete development of a standalone numerical simulation chain, including a multi-scale and multi-physics approach including all simulation steps from particle interactions and radiation environment to circuit electrical response. This chain will be directly used to predict the reliability of a given CMOS digital circuit in a particular radiation environment representative of a specific application. The objective is to accurately model and simulate Single Event Transient (SET) and Single Event Upset (SEU) in progressively scaled CMOS technologies (< 65 nm). SET and SEU will be simulated by Monte Carlo method and simulation results will be validated with experimental data obtained under particles beams. The Monte Carlo simulations will give SEU cross-sections as a function of energy and will provide the transient current parameters that could be an issue for the targeted application. To do so, some basic logical circuits with several to several tens of transistors will be considered. In particular, simulations will be validated by experimental results using integrated technologies (< 65 nm) such as SRAM and some basic logical circuits. In a second part of this work, numerical simulations will be extensively used to propose some iterative improvements in the circuit layouts (for example, moving the locations of the transistors for a given circuit). Some hardness methodology rules will then be given, to determine the layout configuration, which is least sensitive to radiation.

The prediction tools for determining the SEU cross section in SRAM cells will be extremely useful for the design of the SRAM based radiation monitor in P1.5. The study of SET propagation in basic digital cells will be important input for the design of time-based signal processing circuits that will be developed in P2.6. The tools will also prove valuable for the CMOS image sensor which is the topic of P2.11.

Deliverable & Milestones Lists:

- SEU cross sections for the identified technologies.

- SET database for CMOS transistor.

- Report on possible design rules.

- Choice of SRAM devices.

- Choice of logical circuits to be investigated.

- Test bench development.

- Starting SEU and SET Simulation.

- Starting Experimental campaigns.

- Hardening rules investigation.

Beneficiary:

University of Montpellier

Supervisor:

Prof. Frédéric Wrobel (University of Montpellier)

Co-supervisor:

Prof. Jean-Luc Autran (Aix-Marseille University), Prof. Paul Leroux (KU Leuven)

Planned secondments:

[total: 9 months]: AMU (Prof J. L. Autran) [5m] For device technology training and selection and implementation of charge collection mechanisms in design tool; CERN (Dr R. Garcia Alia), RUG (Prof S. Brandenburg), UU (Assoc Prof A. Prokofiev) [2m] For test campaigns; KUL (Dr P. Leroux) [2m] For use and application cases (e.g. SEE monitor)

Position has been appointed to Ygor Aguiar. Click here for Profile.