Short abstract:

The objective of this PhD is to study the correlation between component-level and system-level assessments of the radiation constraint on an intermediate-level electronic board representative of avionic and space computing modules. For system integrators, the standard bottom-up approach for SEE assessment can hardly be used with modern digital integrated circuits, thus methods for assessing the robustness of a digital system by performing system-level testing will be investigated for the very first time at the intermediate scale of a computing board representative for avionic and space on-board computing (OBC) systems based on the latest generation of digital ICs. Both long and short term constraints will be considered by associating accelerated ageing and radiation testing, in connection with the methods developed in WP2. The error margins associated to the system-level approach will be extrapolated both for atmospheric and space environments and the approach relevancy will be compared to the bottom-up reliability methodologies used so far at component level. By establishing a bridge between both levels for one of the most complex and critical sub-system (OBC), this work will pave the way for writing a new industry standard for qualifying the next generation of COTS-based systems exposed to coupled constraints, including those that will be used in large satellite constellations.

Long abstract:

The standard bottom-up approach for SEE assessment in digital systems, starting from the component level to estimate the reliability of a whole system, can hardly be used with modern digital integrated circuits due to the complexity of today’s components. For system integrators, given the cost of extensive testing of FPGA or system-on-chip or microprocessors, and the incomplete knowledge of the ICs' architecture details that prevent low-level analysis of the behavior under radiation, there is a growing interest for system-level reliability characterization. This fact is also motivated by the strong relationship between hardware and software in co-designed computing systems that makes the system-level impact of radiation effects closely dependent on the application. In this project, methods for assessing the robustness of a digital system by performing system-level testing will be investigated at the intermediate scale of a computing board mainly composed of a microprocessor, either an IC or an FPGA, and a mixed-memory environment. One challenge is that such assessment can be extrapolated to potential software evolutions which can occur along the system lifetime to avoid completely new characterizations under beam each time the software is upgraded. The targeted system will be representative for avionic and space on-board computing (OBC) systems. Both long and short term constraints will be considered by associating accelerated ageing and radiation testing, in connection with the methods developed in WP2. This system will be characterized using standard benchmarks as well as a realistic software application. Specific instrumentation at software and RTL level will be developed together with an automated insertion methodology to allow for tracing system faults to component resources. Such tracing will not only provide feedback to system designers but also validate the system-level testing methods by confronting the results with those of WP2. The error margins associated to the system-level approach will be extrapolated both for atmospheric and space environments and the relevancy of the approach will be compared to the bottom-up reliability methodology performed so far at component level. Concerning the relevancy of the test methodology.

Deliverable & Milestones Lists:

- Definition and realization of a “system” board including different kinds of complex digital ICs, with an application software.

- Characterization under coupled radiation and ageing constraints (linked to ESR7 and ESR8) of the system board using particle beams and laser testing.

- System-level fault signatures analysis and tracing methodology

- Confrontation of standard bottom-up reliability predictions with system-level results for different applications and mission profiles

Beneficiary:

University of Montpellier

Supervisor:

Prof. Vincent Pouget (University of Montpellier)

Co-supervisor:

Assoc. Prof. Ketil Røed (Oslo Univeristy).

Planned secondments:

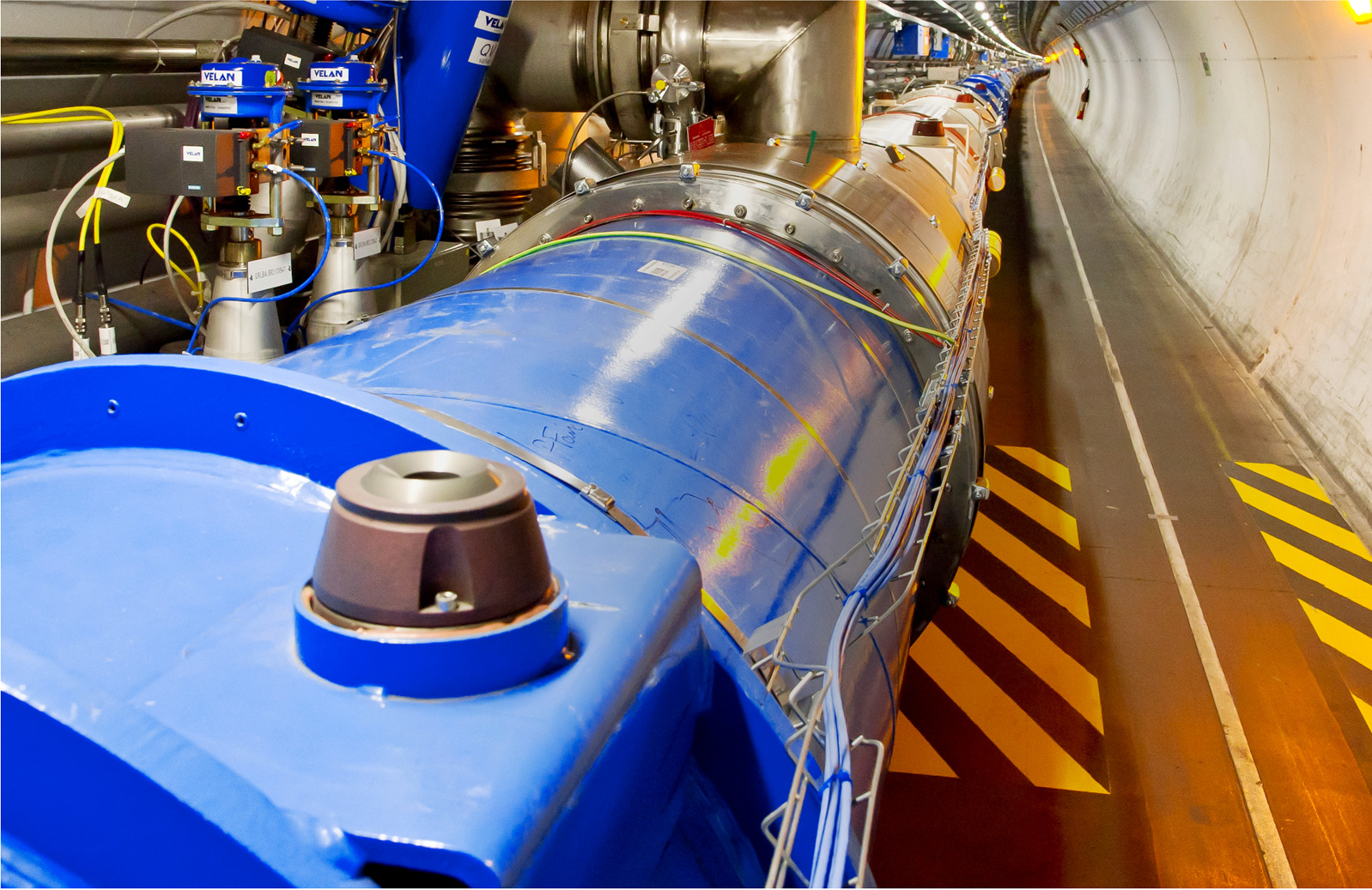

[total: 6 months]: UiO (Assoc. Prof. K. Roed): [2m] for FPGA training and system test preparation; SCK•CEN (Dr W. de Cock), JYU (Dr A. Javanainen), PSI (Dr W. Hajdas) and CERN (Dr R. Garcia Alia): [4m] For radiation testing and setup preparation for 14MeV neutrons and high-energy proton testing as well as dedicated full system tests in representative environments (CHARM).

Position has been appointed to Israel Lopes. Click here for Profile.