Studying electron effectiveness in inducing stuck bits in SDRAMs

Daniel Söderstöm (ESR2) travelled to CERN on September 10-12 for a test campaign dedicated to high energy electrons at the CLEAR facility. This was made possible by the VESPER (The Very energetic Electron facility for Space Planetary Exploration missions in harsh Radiative environments) test instrument. Electrons can be delivered for irradiation of electronics in the 60-200 MeV energy range. Electrons are generated by a laser in pulses of 10-500 pC at a frequency of 3 GHz. The main application of this facility is to allow radiation testing of Single Event Effects for the Jovian environment. It can also be used for assessing Total Ionizing Dose and Displacement Damage effects thanks to the high fluence that can be reached in a short amount of time and the reduced activation.

The aim of Daniel's test was to explore the sensitivity of some digital components to stuck bits induced by high energy electrons. The device that were tested were all SDRAMs (Synchronous Dynamic Random Access Memories). Stuck bits are bits that cannot be written and which thus permanently hold the same binary value. Stuck bits are generated whenever a sufficient amount of displacement damage is caused in the Silicon lattice. Single Event Upsets (SEU) were also observed through out the test, i.e. bit flipping due to energy deposition events to an incorrect value, but that can still be rewritten afterwards. Three memories were tested with differences in the technological CMOS process they were manufactured with. One of such memory was selected by ESA (European Space Agency) for the JUICE mission. The tests were performed on various samples for energies of 60, 120 and 200 MeV with fluxes limited to 50 pC/train. Only the memory with the largest technological node size suffered from Stuck Bits.

ESR15 Andrea Coronetti

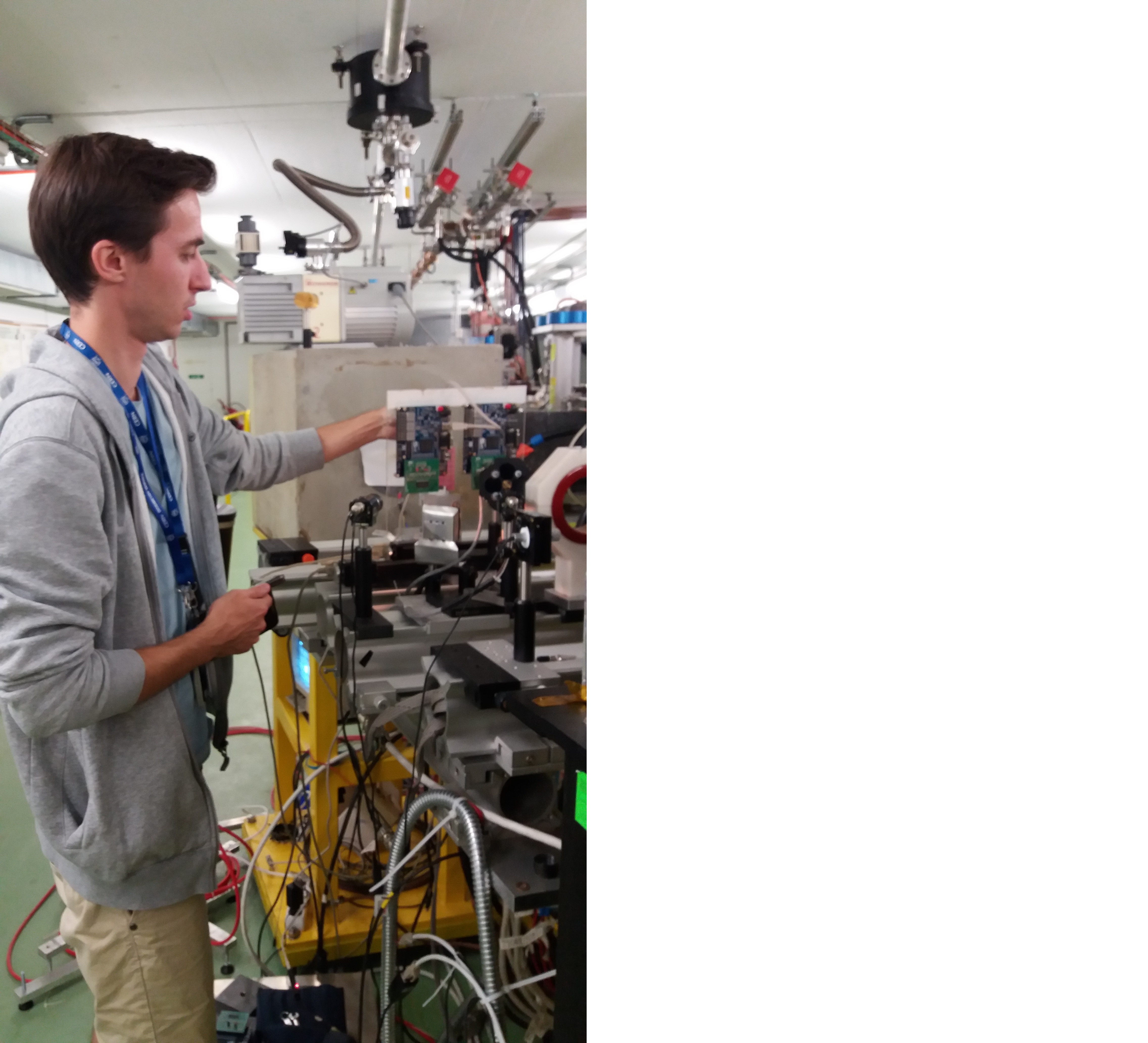

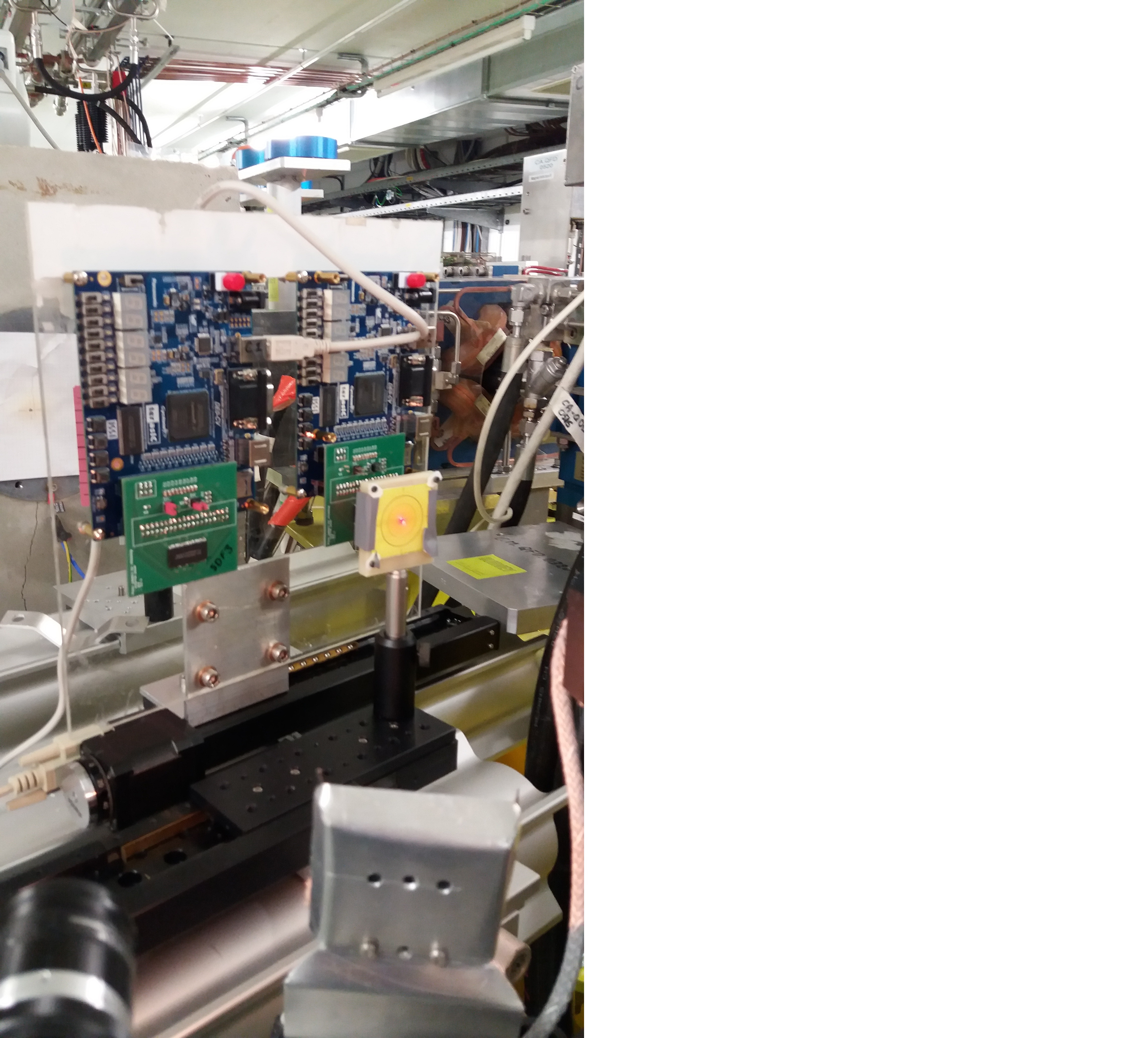

Here are some pictures from the test campaign:

Daniel Söderström mounting the electronic boards in the beamline (Credit: Andrea Coronetti).

The electronic boards are made of a commercial Altera FPGA development board (blue) and some customized PCBs holding the SDRAMs (green) (Credit: Andrea Coronetti).

After running out of components, Daniel soldered new ones (Credit: Andrea Coronetti).